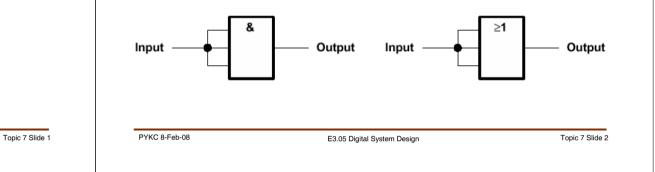

## **Unused inputs (1)**

- All unused inputs of digital logic devices must be connected to a high or low bias to prevent them from floating.

- The logic level that should be applied to any particular unused input depends on the function of the device.

- One solution is to connect unused inputs to an input of the same gate that is in use. Connecting the inputs together increases the capacitive load on the driver stage and, with bipolar circuits, also increases the dc current drain.

# **Unused inputs (2)**

**Topic 7**

**Practical Digital Design:**

I/O interfacing

Peter Cheung Department of Electrical & Electronic Engineering Imperial College London

> URL: www.ee.imperial.ac.uk/pcheung/ E-mail: p.cheung@imperial.ac.uk

> > E3.05 Digital System Design

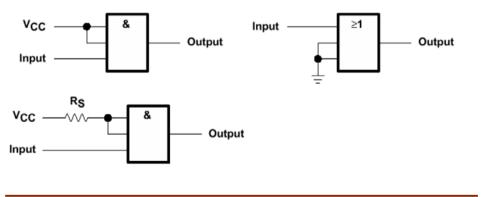

• A better solution is to apply a fixed logic level to the unused inputs. If a low level is required, the input should be directly connected to GND; if a high level is required, it should be connected to the positive supply voltage Vcc directly of via a series resistor.

### **Slow Input Edge Rate**

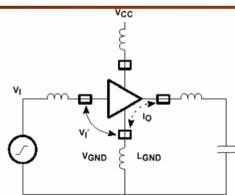

- A slow input edge rate, coupled with the noise generated on the power rails when the output switches, can cause excessive output errors or oscillations.

- Similar situations can occur if an unused input is left floating or is not actively held at a valid logic level.

- These functional problems are due to voltage transients induced on the device's power system.

- In the case of a slowly rising input edge, if the change in voltage at GND is large enough, the apparent signal, V<sub>I</sub>', at the

device appears to be driven back through the threshold and the output starts to switch in the opposite direction.

• If worst-case conditions prevail (simultaneously switching all of the outputs with large transient load currents), the slow input edge is repeatedly driven back through the threshold, causing the output to oscillate.

PYKC 8-Feb-08

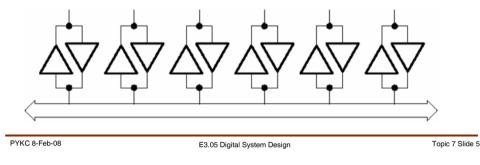

## **Avoid floating inputs**

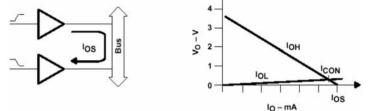

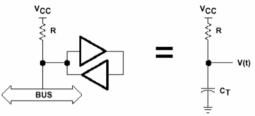

- This is an example of a typical bus system. When all transceivers are inactive, the busline levels are undefined.

- When a voltage that is determined by the leakage currents of each component on the bus is reached, the condition is known as a *floating state*.

- The result is a considerable increase in power consumption and a risk of damaging all components on the bus.

- Holding the inputs or I/O pins at a valid logic level when they are not being used or when the part driving them is in the high-impedance state is recommended.

## Simultaneous Switching Outputs (2)

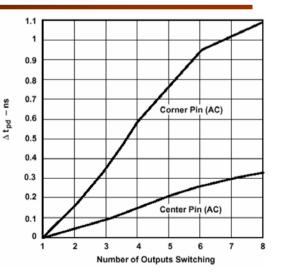

- This figure shows the influence on the delay time of the number of outputs that are switched simultaneously.

- An increase of the delay time of 150 ps to 200 ps for each additional output that is simultaneously switched can be expected.

- With an octal bus driver, such as an SN74xx240, the delay time is increased by 1 ns to 1.4 ns when all eight outputs switch simultaneously.

# Simultaneous Switching Outputs (1)

- The propagation delay times of circuits given in data sheets apply when only **one output switches at a time**. The reason for this is that the production equipment used to test circuits can test only one transmission channel at a time.

- If several outputs switch simultaneously, beware of datasheet!. The reason for this is that the **package inductances** (L<sub>P</sub>) of the supply-voltage lines, as well the output lines (see figure below), have a significant influence on the circuits and, thus, on the delay times.

- These inductances have the effect that the current in the power supply lines, and consequently in the output of the device, has a limited rate of rise.

- When several outputs switch simultaneously, only a limited output current is available.

```

PYKC 8-Feb-08

```

```

E3.05 Digital System Design

```

Topic 7 Slide 6

Cı

Vcc

Lρ

Lp

## **Ground Bounce (1)**

- Ground Bounce is a voltage oscillation between the ground pin on a component package and the ground reference level on the component die.

- Ground Bounce is one of the **primary causes of false switching in high speed components** and is a major cause of poor signal quality.

- Essentially it is caused by a current surge passing through the lead inductance of the package.

- The effect is most pronounced when all outputs switch simultaneously, (hence the alternate name, Simultaneous Switching Noise).

PYKC 8-Feb-08

## **Ground Bounce (2)**

- While the inductance is the combined effect of the package lead, the package lead frame, the bond wire and the inductance in the die pad, most of the inductance is caused by the bond wire.

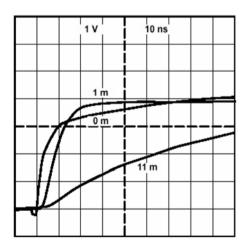

- This figure shows a typical waveform for a high speed CMOS component with TTL level outputs. Shown directly above the signal waveform on the same time scale is the voltage seen on the ground of the die relative to the external ground.

| 0.5             | ⊬   | $\mathbb{A}$            | ⊢         |     | - | ⊢  | ⊢  | ╞         | Die           | Gr  | bund         | uolt          | 100 | ╘         | -   |

|-----------------|-----|-------------------------|-----------|-----|---|----|----|-----------|---------------|-----|--------------|---------------|-----|-----------|-----|

| o lots          | 1   | $\downarrow \downarrow$ | L         |     |   | L_ | L_ | ⊨         |               | Git |              | VOIL          | age | ⊢         |     |

|                 |     | \                       | ν.        | Vol |   |    |    |           |               |     |              |               |     |           |     |

| -0.5            |     |                         |           |     |   |    |    |           |               |     |              |               |     |           |     |

| -1 ⊥            | -   | -                       | I         |     | - | -  | -  |           | L             | L   | -            | -             | -   | -         | _   |

| 3.5 T           | Т   | Г                       |           |     |   |    |    |           |               |     |              |               |     |           |     |

| 3 =             | +   | ⊢                       |           |     |   |    |    | $\vdash$  | -             | _   | $\leftarrow$ | $\overline{}$ | А   |           | =   |

| 2.5             | -1- | -                       |           |     |   |    |    |           | _             | -A  |              | _             |     |           | _   |

| \$ 2 L          |     |                         |           |     |   |    |    |           |               | /   |              |               |     |           |     |

| 2               |     |                         |           |     |   |    |    |           |               |     |              |               |     |           |     |

| Voltage (Volts) |     | V V                     |           |     |   |    |    |           | 1             |     |              |               |     |           |     |

| ∮ 1+            | +   | ╀                       |           |     |   |    |    | $\vdash$  | +             | -   |              | -             |     | $\square$ | -   |

| 0.5             | +   | ₳                       |           |     | _ |    |    |           | $\mathcal{H}$ | _   |              |               |     |           | _   |

| 0+              |     | 11                      | $\square$ |     |   |    |    |           |               |     |              |               |     |           |     |

|                 |     | $  \rangle$             | V         |     |   |    |    |           |               |     |              |               |     |           |     |

| -0.5            |     | Γ                       |           |     |   |    |    |           |               |     |              |               |     |           |     |

| -1 <del> </del> | 0   | 1 2                     |           |     | - |    |    | 8<br>(ns) | 9             | 1   | 0 1          | 1 1           | 2 1 | 3 14      | 1 1 |

### **Ground Bounce (3)**

- Ground Bounce levels are typically more pronounced than Vcc Bounce levels because of the HIGH to LOW transition is trying to quickly bring a HIGH signal down to a narrow window of <400mV for a logic LOW. A low output impedance is required to complete the transition quickly.

- In the LOW to HIGH, the only requirement is that the output be above 2.4V. 5V is available as a driving voltage. A much lower pull up impedance is required to make the transition quickly.

- Ground Bounce effect can be reduced by:

- 1. Using more Vcc/Gnd pins (offered by manufacturers)

- 2. Avoid pullup/pulldown resistors (i.e. use bus hold circuit)

- 3. Possibly use series damping resistors (see later)

- 4. Control output slew rate

- 5. Extra care in holding clock signals to solid voltage level (Vh) and fast clock transistions

| PYKC 8-Feb-08 | E3.05 Digital System Design | Topic 7 Slide 9 | PYKC 8-Feb-08 | E3.05 Digital System Design | Topic 7 Slide 10 |

|---------------|-----------------------------|-----------------|---------------|-----------------------------|------------------|

|               |                             |                 |               |                             |                  |

|               |                             |                 |               |                             |                  |

|               |                             |                 |               |                             |                  |

## **Capacitive Loads or Transmission Line (1)**

- In data sheets, propagation delay times are specified with a capacitive load of 50 pF.

- This value is also the capacitive load when the output drives five inputs of other circuits and this assumes that the length of the connecting lines is only a few centimeters.

- connecting lines is only a few centimeters, as is typically the case on printed circuit boards (PCBs).

- With such short lines, the first assumption is that the line itself behaves like a capacitor, which additionally loads the output and influences the propagation delay time accordingly.

- However, with long lines, this assumption leads to errors, because the signal delay is actually determined by the propagation speed of the electrical wavefront along the line.

- In fact, the propagation delay time of the device is determined by the loading of the output, that is, by the characteristic impedance of the line to which it is connected, not by its length or capacitance.

### **Capacitive Loads or Transmission Line (2)**

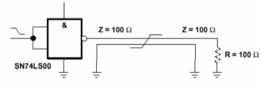

- When driving a line terminated at its end with a resistance of 100Ω, and lengths of 0 (resistor connected directly to the output), 1 m, and 11 m (see below), an SN74LS00 device has the output waveforms shown in this figure.

- The length of the line and the resulting signal propagation time (5 ns/m) influence the delay time of the system. The propagation time of the wave along an 11-m transmission line is 55 ns. Add the propagation delay time of the SN74LS00 of about 10 ns for a total delay of 65 ns.

## **Bus Contention**

• For this short time, a short circuit of the outputs exists, resulting in an overload of the circuit. This situation is known as *bus contention*.

- Bus contention during power-on bus contention that can last several 100 ms

- Even if no defect is detected after such bus contention, a dramatic degradation of the device is likely, which leads to a final destruction of the component some time later.

- Preventing bus contention is not easy.

- One method is to connect a pullup resistor between the enable inputs (assuming low active) of the bus-interface circuits and the positive supply rail.

- A reliable solution is to disable all bus-interface circuits in question during the critical time with additional control logic

| PYKC 8-Feb-08 |  |

|---------------|--|

|---------------|--|

E3.05 Digital System Design

Topic 7 Slide 13

#### **Pullup or Pulldown resistors**

- When buses are disabled for more than the maximum allowable time, other ways should be used to prevent components being damaged or overheated.

- A pullup or a pulldown resistor to  $V_{CC}$  or GND, respectively, should be used to keep the bus in a defined state. The size of the resistor plays an important role

and, if its resistance is not chosen properly, a problem occur.

- Usually, a 1-kΩ to 10-kΩ resistor is recommended. The maximum input transition time must not be violated selecting pullup or pulldown resistors. Otherwise, components may oscillate, or device reliability may affected.

- This pullup resistor method is recommended for ac-powered systems; however, it is not recommended for battery-operated equipment because power consumption is critical.

- Instead, use the **bus-hold** feature that is discussed in the next section. The overall advantage of using pullup resistors is that they ensure defined levels when the bus is floating and help eliminate some of the line reflections, because resistors also can act as bus terminations.

```

PYKC 8-Feb-08

```

PYKC 8-Feb-08

E3.05 Digital System Design

Topic 7 Slide 14

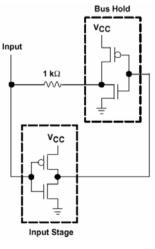

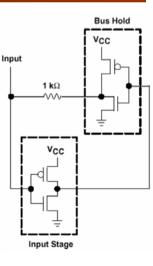

# **Bus Hold Circuit**

- Bus-hold circuits are used in selected TI families to help solve the floating-input problem and eliminate the need for pullup and pulldown resistors.

- Bus-hold circuits consist of two back-to-back inverters with the output fed back to the input through a resistor (see Figure 4.17).

- To understand how the bus-hold circuit operates, assume that an active driver has switched the line to a high level. This results in no current flowing through the feedback circuit.

- Now, the driver goes to the high-impedance state and the bushold circuit holds the high level through the feedback resistor.

- The current requirement of the bus-hold circuit is determined only by the leakage current of the circuit.

- The same condition applies when the bus is in the low state and then goes inactive.

#### **Bus Hold Circuit**

- Bus-hold circuits are used in selected TI families to help solve the floating-input problem and eliminate the need for pullup and pulldown resistors.

- Bus-hold circuits consist of two back-to-back inverters with the output fed back to the input through a resistor (see Figure 4.17).

- To understand how the bus-hold circuit operates, assume that an active driver has switched the line to a high level. This results in no current flowing through the feedback circuit.

- Now, the driver goes to the high-impedance state and the bushold circuit holds the high level through the feedback resistor.

- The current requirement of the bus-hold circuit is determined only by the leakage current of the circuit.

- The same condition applies when the bus is in the low state and then goes inactive.

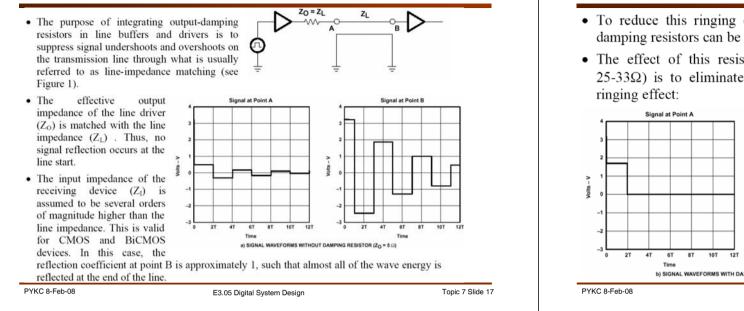

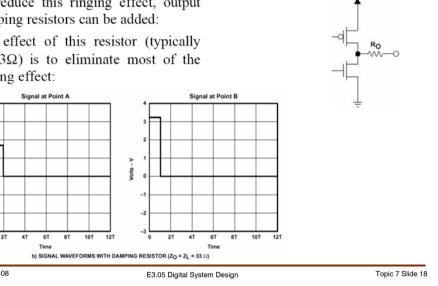

### Series Damping Resistor (1)

## Series Damping Resistor (2)

- To reduce this ringing effect, output damping resistors can be added:

- The effect of this resistor (typically 25-33 $\Omega$ ) is to eliminate most of the

# FPGAs provides many of these functions (1)

• Here is a summary of different terminations that may be programme on a

typical FPGA I/O block (example taken from Xilinx). **Double Parallel Terminated** Unterminater Unterminated Output Driving Series Terminated Output Driving a Parallel Terminated Input a Parallel Terminated Input Series-Parallel Terminated Output Driving a Parallel Terminated Input Series Terminated Output

## Modern Electronics I/O Standards

- Modern digital electronics use many different I/O standards.

- Here is an incomplete list:

- LVTTL Low-voltage TTL

- LVCMOS2 Low-voltage CMOS for 2.5v

- PCI Peripheral Component Interface

- GTL Gunning Transceiver Logic (Terminated)

- GTL+ Gunning Transceiver Logic Plus

- HSTL High-Speed Transceiver Logic

- SSTL2 Stub Series Terminated Logic for 2.5v

- SSTL3 Stub Series Terminated Logic for 3.3v

- LVDS Low Voltage Differential Signals

- AGP Advanced Graphics Port

PYKC 8-Feb-08

The following specifications of these standards refer to those used by Xilinx in their Virtex family of FPGAs.

E3.05 Digital System Design

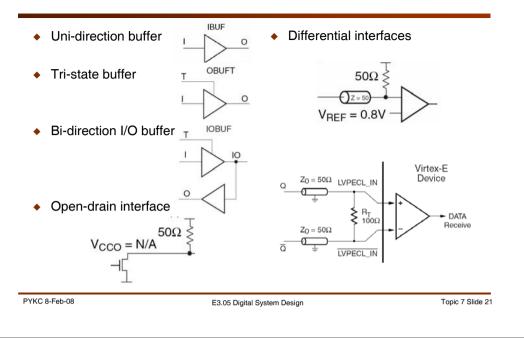

# **Types of I/O**

## LVCMOS2 — Low-Voltage CMOS for 2.5 Volts

- The LVCMOS2 standard is an extension of the LVCMOS standard used for general purpose 2.5V applications.

- It uses a 5V tolerant CMOS input buffer and a Push-Pull output buffer. This standard requires a 2.5V output source voltage (VCCO), but does not require the use of a reference voltage (VREF) or a board termination voltage (VTT).

| Parameter                               |                         | Min  | Тур | Max |

|-----------------------------------------|-------------------------|------|-----|-----|

| V <sub>CCO</sub>                        |                         | 2.3  | 2.5 | 2.7 |

| V <sub>REF</sub>                        |                         |      | -   | -   |

| V <sub>TT</sub>                         |                         |      | -   | -   |

| V <sub>IH</sub>                         | Virtex                  | 1.7  | -   | 5.5 |

|                                         | Virtex-E &<br>Virtex-EM | 1.7  | -   | 3.6 |

| V <sub>IL</sub>                         |                         | -0.5 | -   | 0.7 |

| V <sub>OH</sub>                         |                         | 1.9  | -   | -   |

| V <sub>OL</sub>                         |                         | -    | 0.4 |     |

| I <sub>OH</sub> at V <sub>OH</sub> (mA) | -12                     | -    | -   |     |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) |                         | 12   | -   | -   |

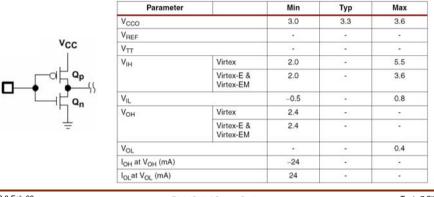

## LVTTL — Low-Voltage TTL

- The LVTTL standard is a general purpose EIA standard for 3.3V applications that uses an LVTTL input buffer and a Push-Pull output buffer.

- The input and output buffers are both 5V-tolerant. This standard requires a 3.3V output source voltage (VCCO), but does not require the use of a reference voltage (VREF) or a termination voltage (VTT).

PYKC 8-Feb-08

E3.05 Digital System Design

Topic 7 Slide 22

## **GTL** — Gunning Transceiver Logic Terminated

- The GTL standard is a high-speed bus standard invented by Xerox.

- Many FPGA companies have implemented the terminated variation for this standard, requiring a differential amplifier input buffe

VTT = 1.2V  $V_{TT} = 1.2V$ 50Ω Š 50Ω Š  $V_{CCO} = N/A$  $V_{\text{DEE}} = 0.8V$

| output buffer. |  |

|----------------|--|

|                |  |

|                |  |

| Parameter                                       | Min  | Тур  | Max  |

|-------------------------------------------------|------|------|------|

| V <sub>cco</sub>                                | 2    | N/A  |      |

| $V_{REF} = N \times V_{TT}^{1}$                 | 0.74 | 0.8  | 0.86 |

| V <sub>TT</sub>                                 | 1.14 | 1.2  | 1.26 |

| $V_{IH} \ge V_{REF} + 0.05$                     | 0.79 | 0.85 |      |

| $V_{IL} \le V_{REF} - 0.05$                     | -    | 0.75 | 0.81 |

| V <sub>OH</sub>                                 | •    | -    |      |

| V <sub>OL</sub>                                 | •    | 0.2  | 0.4  |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)         | -    | -    |      |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.4V | 32   | •    |      |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.2V | -    | -    | 40   |

PYKC 8-Feb-08

Topic 7 Slide 23

PYKC 8-Feb-08

#### **GTL+**— Gunning Transceiver Logic Plus

| ndard derived from GTL, first<br>Pentium Pro processor. | •    | $D = \frac{50\Omega}{V_{RE}}$ | $50\Omega$ |   |

|---------------------------------------------------------|------|-------------------------------|------------|---|

| Parameter                                               | Min  | Тур                           | Max        | ] |

| V <sub>CCO</sub>                                        | -    | -                             | -          | 1 |

| $V_{REF} = N \times V_{TT}^{1}$                         | 0.88 | 1.0                           | 1.12       | 1 |

| V <sub>TT</sub>                                         | 1.35 | 1.5                           | 1.65       | 1 |

| $V_{IH} \ge V_{REF} + 0.1$                              | 0.98 | 1.1                           | -          | 1 |

| $V_{IL} \le V_{REF} - 0.1$                              | -    | 0.9                           | 1.02       | 1 |

| V <sub>OH</sub>                                         | -    | -                             | -          | 1 |

| V <sub>OL</sub>                                         | 0.3  | 0.45                          | 0.6        | 1 |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)                 | -    | -                             | -          | 1 |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.6V         | 36   | -                             | -          | 1 |

| I <sub>OL</sub> at V <sub>OL</sub> (mA) at 0.3V         | -    | -                             | 48         | 1 |

#### SSTL3 — Stub Series Terminated Logic for 3.3V

| • | A general purpose 3.3'<br>standard sponsored by<br>This standard has two<br>This standard requires<br>Amplifier input buffer a<br>output buffer. | Hitachi and IBM.<br>classes, I and II.<br>a Differential |                  | $V_{TT} = 1.5V V$ $50\Omega \neq 50$ $V_{REF} = 0.9$ |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|------------------------------------------------------|--|

|   | Parameter                                                                                                                                        | Min                                                      | Тур              | Max                                                  |  |

|   | V <sub>cco</sub>                                                                                                                                 | 1.40                                                     | 1.50             | 1.60                                                 |  |

|   | V <sub>REF</sub>                                                                                                                                 |                                                          | 0.90             |                                                      |  |

|   | V <sub>TT</sub>                                                                                                                                  |                                                          | V <sub>CCO</sub> |                                                      |  |

|   | V <sub>IH</sub>                                                                                                                                  | V <sub>REF</sub> + 0.1                                   |                  |                                                      |  |

|   | VIL                                                                                                                                              |                                                          |                  | $V_{REF} - 0.1$                                      |  |

|   | V <sub>OH</sub>                                                                                                                                  | V <sub>CCO</sub> - 0.4                                   |                  |                                                      |  |

|   | V <sub>OL</sub>                                                                                                                                  |                                                          |                  | 0.4                                                  |  |

|   | I <sub>OH</sub> at V <sub>OH</sub> (mA)                                                                                                          | -8                                                       | -                | -                                                    |  |

|   | I <sub>OL</sub> at V <sub>OL</sub> (mA)                                                                                                          | 48                                                       | -                | -                                                    |  |

#### PYKC 8-Feb-08

#### Topic 7 Slide 27

## HSTL — High-Speed Transceiver Logic

The HSTL standard is a general purpose high-speed, 1.5V bus standard sponsorec V<sub>TT</sub>= 1.5V V<sub>TT</sub>= 1.5V 50Ω≶ 50Ω≶ by IBM and has four variations or classes. This standard requires a Differential  $V_{BEF} = 0.9V$ Amplifier input buffer and a Push-Pull output buffer. HSTL Class IV Voltage Specification Parameter Min Max Тур Vcco 1.40 1.50 1.60 0.90 VREF

V<sub>BEF</sub> + 0.1

$V_{CCO} - 0.4$

-8

48

Vcco

-

-

PYKC 8-Feb-08

$V_{TT}$

$V_{IH}$

$V_{IL}$

VOH

VOL

IOH at VOH (mA)

I<sub>OL</sub>at V<sub>OL</sub> (mA)

E3.05 Digital System Design

Topic 7 Slide 26

#### SSTL3 — Stub Series Terminated Logic for 3.3V

- A general purpose 3.3V memory bus standard sponsored by Hitachi and IBM.

- This standard has two classes, I and II.

- This standard requires a Differential Amplifier input buffer and an Push-Pull οι SSTL3\_II Voltage Specifications

| V <sub>CCO</sub> = 3.3V | V <sub>TT</sub> = 1.5V V <sub>TT</sub> = 1.5V<br>⊤ ⊤ ⊤<br>50Ω ≤ 50Ω ≤ |  |

|-------------------------|-----------------------------------------------------------------------|--|

|                         | V <sub>REF</sub> = 1.5V                                               |  |

V<sub>REF</sub> - 0.1

0.4

-

-

|       | -    |       | <br>- |  |

|-------|------|-------|-------|--|

| utput | t bu | ffer. |       |  |

| Parameter                                     | Min     | Тур | Max   |

|-----------------------------------------------|---------|-----|-------|

| V <sub>CCO</sub>                              | 3.0     | 3.3 | 3.6   |

| $V_{\text{REF}} = 0.45 \times V_{\text{CCO}}$ | 1.3     | 1.5 | 1.7   |

| V <sub>TT</sub> = V <sub>REF</sub>            | 1.3     | 1.5 | 1.7   |

| $V_{IH} \ge V_{REF} + 0.2$                    | 1.5     | 1.7 | 3.9(1 |

| $V_{IL} \le V_{REF} - 0.2$                    | -0.3(2) | 1.3 | 1.5   |

| $V_{OH} \ge V_{REF} + 0.8$                    | 2.1     | 2.3 | -     |

| $V_{OL} \leq V_{REF} - 0.8$                   | -       | 0.7 | 0.9   |

| I <sub>OH</sub> at V <sub>OH</sub> (mA)       | -16     | -   | -     |

| I <sub>OL</sub> at V <sub>OL</sub> (mA)       | 16      | -   | -     |

PYKC 8-Feb-08

E3.05 Digital System Design

#### V<sub>TT</sub>= 1.25V The SSTL2 standard is the same as $V_{CCO} = 2.5V$ SSTL3. but for 2.5V. $50\Omega \leq$ There are also two classes: I & II. $25\Omega$ NAA. -)Z = 50 $V_{REF} = 1.25V$ Terminated SSTL2 Class I Parameter Min Max Тур 2.3 2.5 2.7 Vcco $V_{\text{BEF}} = 0.5 \times V_{\text{CCO}}$ 1.15 1.25 1.35 $V_{TT} = V_{BEF} + N^{(1)}$ 1.25 1.11 1.39 $V_{IH} \ge V_{REF} + 0.18$ 3.0(2) 1.33 1.43 $V_{IL} \leq V_{REF} - 0.18$ $-0.3^{(3)}$ 1.07 1.17 $V_{OH} \ge V_{REF} + 0.61$ 1.76 1.82 1.96 $V_{OL} \le V_{REF} - 0.61$ 0.54 0.64 0 74 I<sub>OH</sub> at V<sub>OH</sub> (mA) -7.6 --I<sub>OL</sub>at V<sub>OL</sub> (mA) 7.6 --PYKC 8-Feb-08 Topic 7 Slide 29 E3.05 Digital System Design

SSTL2 — Stub Series Terminated Logic for 2.5V

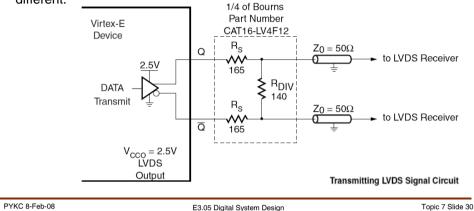

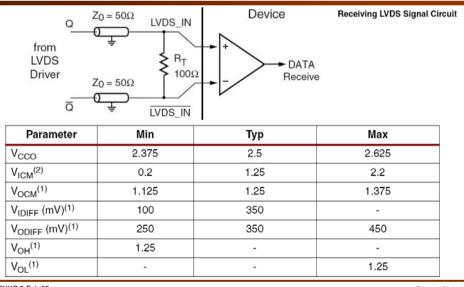

## LVDS – Low voltage differential signal (1)

- This is a fully differential signals often used for very high speed network connections.

- The transmit and receive circuits are different.

## LVDS – Low voltage differential signal (2)

## FPGAs provides many of these functions (2)

- Other programmable features (in addition to termination) are:

- Input Reference Voltage (Vref)

- Output Source Voltage (Vcco)

- Board Termination Voltage (Vtt)

- Output Slew Rate

- Output Drive Strength

- Synchronous/Asynchronous I/O

- Programmable Output Delay (called ChipSynch in Xilinx)

### Xilinx Virtex 5 I/O capability

### **Altera Cyclone-II I/O Features**

# I/O Structure &

#### **Features**

IOEs support many features, including:

2.5-V LVTTL/LVCMOS 1.8-V LVTTL/LVCMOS Differential and single-ended I/O standards 1.5-V LVCMOS 3.3-V, 64- and 32-bit, 66- and 33-MHz PCI compliance LVDS RSDS Joint Test Action Group (JTAG) boundary-scan test (BST) support mini-LVDS Output drive strength control LVPECL (3) Weak pull-up resistors during configuration SSTL-2 Class I and II Tri-state buffers SSTL-18 Class I **Bus-hold** circuitry HSTL-18 Class I Programmable pull-up resistors in user mode HSTL-15 Class I Programmable input and output delays Differential SSTL-2 (4) Open-drain outputs Differential SSTL-18 (4) DQ and DQS I/O pins Differential HSTL-18 (5) V<sub>REF</sub> pins Differential HSTL-15 (5)

```

PYKC 8-Feb-08

```

E3.05 Digital System Design

Topic 7 Slide 34

All I/O Banks Support

3.3-V LVTTL/LVCMOS

#### Each pin can be input and (3-state-able) output

- Each pin can be individually configured for:

- ChipSync, XCITE termination, drive strength, input threshold, weak pull-up or down

- Each input can be 3.3-V tolerant, limited by its Vcco

- No 5-V tolerance, unless current-limiting R is used

- Each I/O can have the same performance

- Up to 700 Mbps single-ended & 1.25 Gbps differential LVDS

- Each I/O supports 40+ voltage and protocol standards including:

| <ul> <li>LVCMOS (<i>3.3v</i>, 2.5v, 1.8v, 1.5v, and <i>1.2v</i>)</li> <li>LVDS, Bus LVDS, Extended LVDS</li> <li>LCPECL</li> <li>PCI, PCI-X</li> <li>HyperTranport (LDT)</li> </ul> | <ul> <li>HSTL (1.8v, 1.5v, Classes I, II, III, IV)</li> <li>HSTL_I_12 (unidirectional only)</li> <li>DIFF_HSTL_I_18,<br/>DIFF_HSTL_I_18, DCI</li> <li>DIFF_HSTL_I, DIFF_HSTL_I_DCI</li> <li>RSDS_25 (point-to-point)</li> </ul> | <ul> <li>SSTL (2.5v, 1.8v, Classes I, II)</li> <li>DIFF_SSTL_I</li> <li>DIFF_SSTL2_I_DCI</li> <li>DIFF_SSTL18_I,<br/>DIFF_SSTL18_I_DCI</li> <li>GTL, GTL+</li> </ul> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PYKC 8-Feb-08                                                                                                                                                                       | E3.05 Digital System Design                                                                                                                                                                                                     | Topic 7 Slide 33                                                                                                                                                     |

## **Useful References**

- Application Notes SDYA009C, "Designing with Logic", Texas Instrument, June 1997.

- XAPP133, "Using the Virtex Select I/O Resource", Xilinx.

- Cyclone II Device Handbook, Vol. 1, p. 2-37 to 2-61.